# **CARLOS v5 reference manual**

Samuele Antinori, Filippo Costa, Davide Falchieri, Alessandro Gabrielli, Enzo Gandolfi, Massimo Masetti, Samuele Zannoli

Department of Physics and INFN Bologna

# **Outline**

| What's new in CARLOS v5                     | 3  |

|---------------------------------------------|----|

| CARLOS v5 main features                     | 4  |

| General chip description                    | 8  |

| SDD readout chain.                          | 8  |

| CARLOS architecture                         | 8  |

| Main processing unit                        | 12 |

| 2D compressor block                         | 13 |

| Disabling the 2D compressor                 | 14 |

| End of Row Summary                          | 14 |

| Data transmission protocol                  | 16 |

| JTAG mode                                   | 16 |

| RUN mode                                    | 18 |

| Error flag words                            | 19 |

| CARLOS v5 pin position and function         | 22 |

| Programming CARLOS v5                       |    |

| Controlling CARLOS via the serial back-link | 25 |

| Opening a JTAG connection                   | 27 |

| CARLOS internal registers                   | 29 |

| Register access via the JTAG bus            | 30 |

| Board level testing via JTAG                | 34 |

| Chip level testing via JTAG                 | 35 |

| Running CARLOS v5                           |    |

| How to run CARLOS v5                        | 36 |

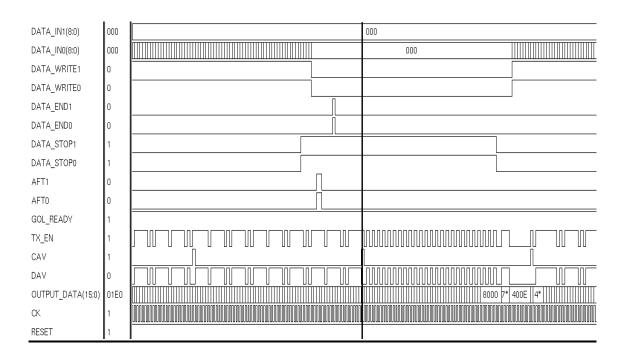

| Managing synchronization errors             | 45 |

| Stop If Error = 1                           | 45 |

| Stop If Error = 0.                          | 47 |

| Notes                                       |    |

| Backpressure from CARLOSrx to CARLOS        | 50 |

| Debugging CARLOS v5                         | 51 |

| Debugging facility                          | 51 |

| BIST                                        | 51 |

| Analyzing CARLOS v5                         | 52 |

| Why parsepack?                              | 52 |

| How to get parsepack                        |    |

| How to compile parsepack                    | 53 |

| How to use parsepack                        |    |

| What are parsepack outputs?                 | 56 |

# What's new in CARLOS v5

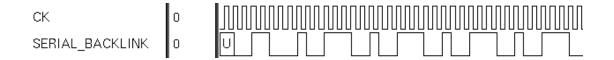

- The *ck* and *serial backlink* CARLOS input pads have been converted from CMOS to LVDS.

- Two new LVDS ck out signals have been added: ck out LH and ck out RH.

- A new input pin has been added to CARLOS: the *locked* pin. The *locked* signal is driven by the QPLL device: when 1 the QPLL is locked to the incoming clock and it provides a low-jitter clock to CARLOS and GOL, otherwise the QPLL is out of lock and the transmission should be stopped. The *locked* signal has been put in AND with the *gol\_ready* internally to CARLOS, so if one of the two signals is not active, the transmission is immediately stopped.

- The test pins have been reduced from 11 to 4 pins (2 for set\_test and 2 for test output).

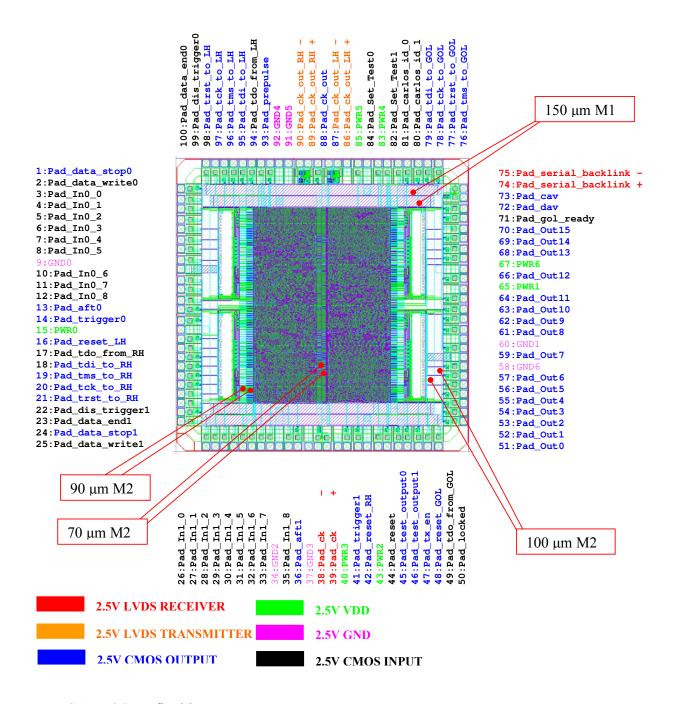

- The pad order has completely changed with respect to the previous versions: so far CARLOS v5 is NOT pad compatible with CARLOS v4 and CARLOS v3.

- The size of *fifo\_data* has been extended from 24 to 26 30-bits words. Furthermore the *almost\_full* flag (and consequently the *data\_stop* CARLOS output) is asserted when the FIFO contains only 5 empty locations.

- The boundary scan register has been modified according to the changes in the pinout. In particular the order of the boundary scan cells has changed and the total number has been reduced from 82 to 76.

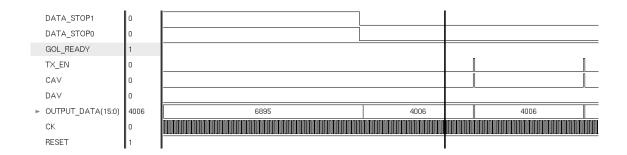

- In CARLOS v4 each *data\_stop* output is put to 0 at the end of an event after the corresponding FIFO has been completely emptied (some clock periods before CARLOS output data packet has been closed with the 3 footer words). So far if the input gol\_ready goes to 0, a new event coming from AMBRA is processed and stored in the FIFO before the previous one has been closed, giving rise to a possible error. In CARLOS v5 each *data\_stop* output is put to 0 only after the output data packet has been closed by sending the 3 footer words.

- In CARLOS v4 a situation may happen in which an internal signal notifying that both FIFOs have been emptied occurs when the incoming signal *gol\_ready* is 0: in this case the signal is ignored and two consecutive events are merged into one. CARLOS v5 has corrected this situation by taking into account the signal value regardless of the *gol\_ready* signal value.

- In CARLOS v4 the error flag word values are updated one every 64 clock cycles regardless of the *gol\_ready* value. So far when the *gol\_ready* value is 0, some important information such as an acknowledgement could be lost. In CARLOS v5 the error flag word values are updated one every 64 clock cycles only when the *gol\_ready* signal is 1.

# **CARLOS v5 main features**

- 4x4 mm<sup>2</sup>, 100 pins, CERN 0.25 μm CMOS technology.

- 17k gates + four 256x9-bit SRAM blocks.

- 2.5V Power Supply.

- 200mA @ 40MHz.

- double threshold 2D compression on input data; if desired, compression may be disabled and, in this case, a simple 1D encoding is performed on incoming data.

- 40 MHz target working frequency.

- interface to GOL implemented using both Ethernet and G-Link protocols.

- standard IEEE 1149.1 JTAG implemented.

- BIST implemented using 400 pseudo-random test vectors.

- the JTAG port input values are decoded and delivered either towards CARLOS itself, or towards the left or right hybrid (a board containing 4 PASCAL-AMBRA pairs used to acquire data coming from a half-detector SDD), or towards the GOL chip.

- JTAG answer *tdo* and output data share the same 16-bit data channel towards the GOL chip.

- JTAG mode and RUN mode are mutually exclusive in time: it means that when in JTAG mode, the normal behavior of the chip is frozen and vice-versa. CARLOS working mode is determined by the commands "Enter JTAG mode" and "Enter RUN mode" that CARLOSrx sends to CARLOS via the serial back-link.

- adoption of measures against radiation effects: parity errors on RAM words and on JTAG configurable registers are asserted in the error flag words put in output. The same holds also for parity errors detected on AMBRA. Besides that parity errors are also notified in the End Of Row Summaries.

Fig. 1: CARLOS v5 final layout

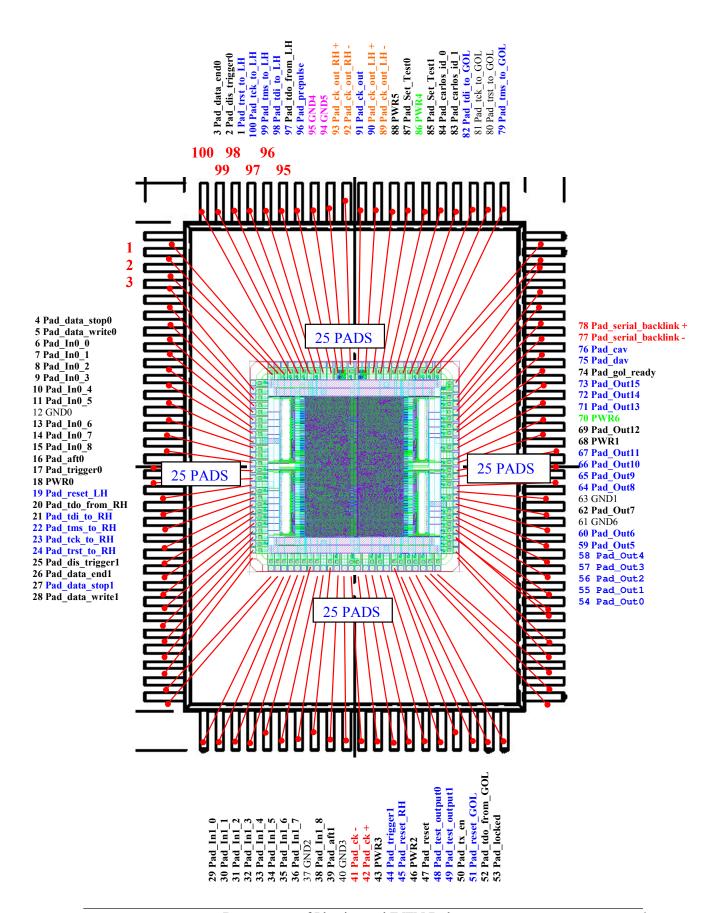

Fig. 2: SDD readout chain

# **General chip description**

## **SDD** readout chain

CARLOS v5 is an ASIC belonging to the SDD readout chain, as shown in Fig. 2. The chip is directly interfaced to different devices:

- <u>2 hybrids</u>: an hybrid is a board containing 4 PASCAL AMBRA pairs, being the front-end electronics acquiring data coming from a half-detector;

- <u>GOL</u>: a rad-hard serializer chip sending data to CARLOSrx by means of a 800 Mbit/s optical link. The GOL requires a very low-jitter clock (max 100 ps peak to peak): such a clock is sent to GOL using the QPLL device.

- <u>CARLOSrx</u>: an FPGA-based device put in counting room with the purpose of collecting data coming from different SDD chains and sending them towards the DDL system. Besides that it remotely controls CARLOS using a 40 MHz serial back-link for what concerns CARLOS working mode and JTAG programming. It also manages the interface between CARLOS and the CTP system and the TTCrx device, transferring trigger signals from the TTCrx to CARLOS on the serial back-link and transferring the busy signal from CARLOS towards the CTP. For more details on CARLOSrx see the document *carlosrx\_datasheet.pdf* available at the following Web site: <a href="http://www.bo.infn.it/~falchier/alice.html">http://www.bo.infn.it/~falchier/alice.html</a>.

This document refers to the CARLOSrx device used at the August 2003 CERN test beam.

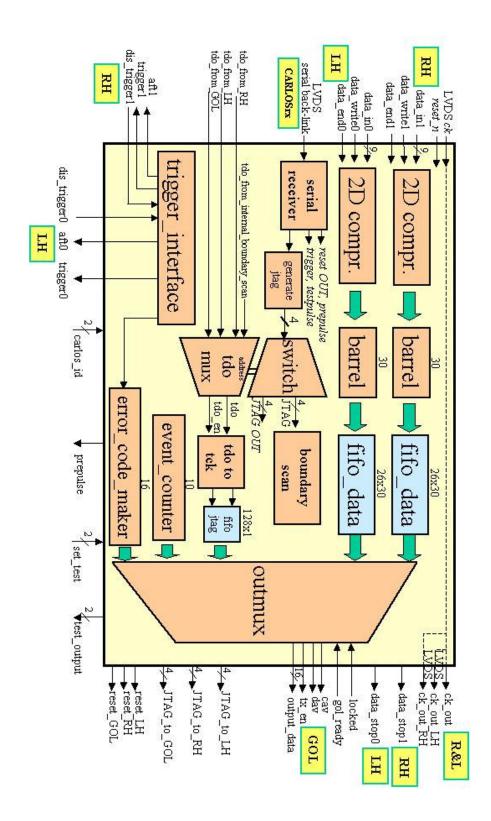

# **CARLOS** architecture

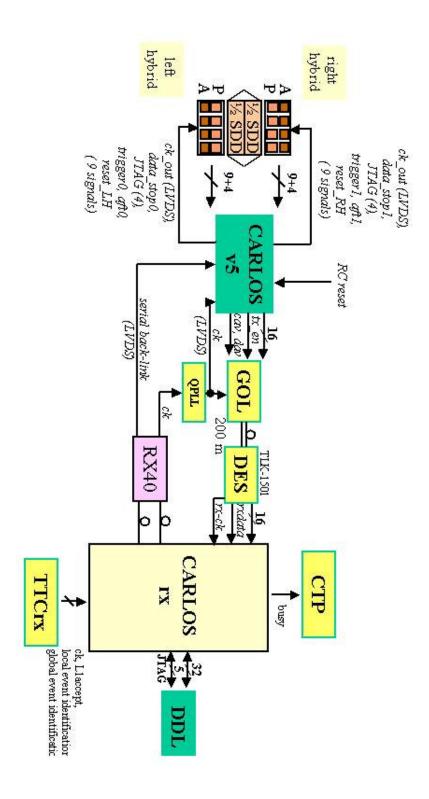

The purpose of CARLOS v5 is to perform an on-line 2D compression on two incoming 8-bit data streams from the two hybrids, one for each half-detector. Compressed data are then packed in 30-bit long words using a barrel shifter, temporarily stored in a 26x30 flip-flop based FIFO and then multiplexed on a single 16-bit bus output towards the serializer GOL chip (see CARLOS architecture in Fig. 3). The two data channels are processed in parallel and, in each data processing channel, compression, packing and storing steps are performed as successive stages of a pipeline with a clock running at 40 MHz.

Compression performances are completely tunable using a set of registers that can be programmed using a standard JTAG access port. Using this port, 2D compression itself can be switched on or off and threshold levels can be modified by writing and reading internal configuration registers only when CARLOS is in JTAG working mode. Beside that, internal registers are protected against the radiation effects using a parity mechanism: each time a register is accessed, parity is computed and compared with the expected value. In case a mismatch is found, it is reported in the End Of Row Summary at the end of each processed anode. In case a severe parity violation if

found, an error flag is switched on in the output data sent to CARLOSrx through the optical link, so to allow CARLOSrx to program CARLOS internal registers again the sooner the possible. The CARLOSrx device remotely controls CARLOS v5 via a synchronous serial back-link.

CARLOS provides both clock signal and the JTAG signals to the left and right hybrids. The  $ck\_out$  CMOS output pad is directly connected to the ck input: it is used to provide the clock to AMBRA and PASCAL. If needed the LVDS  $ck\_out\_LH$  and  $ck\_out\_RH$  output pads can be used as well.

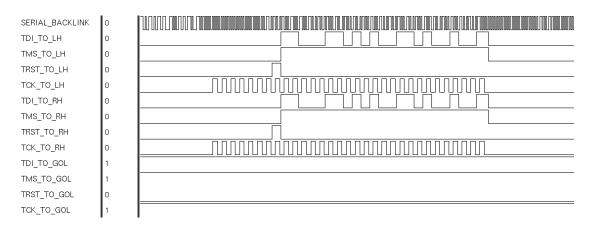

For what concerns JTAG, CARLOS also acts as a JTAG switch providing 3 4-bits JTAG ports in output: one for the left hybrid, one for the right hybrid and one for the GOL chip. In other words CARLOS receives the JTAG port signals encapsulated over the serial back-link and provides in output 3 JTAG ports, thus allowing to open a JTAG connection towards different devices.

The mechanism is the following one: after receiving the *trst* signal on the serial backlink channel, CARLOS begins waiting for a 7-bit address (encoded with redundancy and parity protected) containing the information of which is the device to be addressed via JTAG. After decoding the address, JTAG information can be switched to CARLOS itself, to the right hybrid, to the left hybrid or to the GOL chip, so far providing JTAG connectivity towards PASCAL, AMBRA, CARLOS and GOL chips. The JTAG connection can then be closed by asserting the *trst* signal again over the serial back-link channel or by resetting CARLOS (beside closing the JTAG connection a reset action also resets all the internal register, so it is neither a good practice nor useful to close a JTAG connection in this way).

CARLOS v5 can work in two distinct and non-overlapping in time working modes, JTAG mode and RUN mode. After a reset action CARLOS is put in JTAG mode, then it can be put in RUN mode by sending the command "Enter RUN mode" on the serial back-link: in the same way when in RUN mode, CARLOS is put in JTAG mode when receiving the command "Enter JTAG mode".

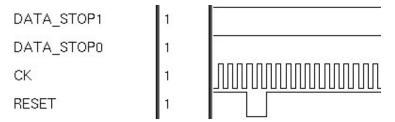

• When in JTAG mode, CARLOS can not process neither any input data from AMBRA (data\_stop1 and data\_stop0 outputs are kept high) nor any trigger input command (when CARLOS is in JTAG mode, CARLOSrx itself has to provide a busy = 1 towards the CTP system): only reset and JTAG commands are processed. After CARLOSrx opens a JTAG connection towards one of the hybrids or the GOL, the selected device begins sending the JTAG answer on their output pins tdo (from CARLOS point of view: tdo\_from\_LH, tdo\_from\_RH, tdo\_from\_GOL). CARLOS samples the tdo values coming from the selected device when they are valid and sends them towards CARLOSrx using the 16-bit output data bus, the same used for sending data and error flags words when in RUN mode.

After CARLOSrx opens a JTAG connection towards CARLOS itself, CARLOS internal JTAG answer *tdo* is sampled and put in output over the 16-bit output bus. In each case the *tdo* value (either coming from outside or computed internally on CARLOS) is sampled only in the JTAG standard states **Shift-IR**

and **Shift-DR**. In the former case the *tdo* output is 1000...0 serially shifted out (the code length is the same as the number of bits of the JTAG Instruction Register). In the latter case the *tdo* output contains the value of the selected internal register serially shifted out (so far the old register content before being written again).

When a broadcast JTAG operation is performed (more than one chip JTAG-addressed at the same time), no *tdo* value is sampled by CARLOS (CARLOS does not receive any information on whether the operation has been successful or not), in fact in this case more than one chip would be driving CARLOS *tdo* input signal, resulting in a bus contention.

In case CARLOSrx tries to open a JTAG connection towards a device without success, it will not receive the expected answer on the JTAG word, so that it will try to open the JTAG connection again, after a time-out period. No error code concerning the impossibility of opening a JTAG connection has been foreseen.

When in RUN mode, CARLOS processes data coming from AMBRA and trigger commands coming from CARLOSrx over the serial back-link channel. Data words sent towards the GOL chip contain both processed data and error flag words encapsulated in a protocol compliant both with G-Link and Ethernet standard modes.

CARLOS v5 also hosts a BIST (Built In Self Test) facility in order to ease the chip test and selection: after running the JTAG RUNBIST command, 400 test vectors are fed into the 2 processing channels. Data coming out from the multiplexer block *Outmux* are then analyzed by a *Signature Maker* block performing a deterministic function of its inputs and producing a 16-bit code strictly dependent on its input data. This code can then be read using the standard JTAG port in order to check whether the chip has passed the test or not. It is a pass / no pass test: it gives no indication of where the failure happens, if any.

An other test facility hosted on CARLOS is a multiplexer bringing in output the values of key internal nets, such as the output of the compressor block or the barrel shifter, in order to ease the chip debugging phase. The multiplexer selection lines are directly driven by the 3-bit input bus *set test*.

Fig. 3: CARLOS v5 schematic blocks

## Main processing unit

The main processing unit of CARLOS v5 is composed by 3 main logic blocks (see Fig. 3):

- 2D compressor

- barrel shifter

- fifo\_data

The 2D compressor implements a bi-dimensional double threshold compression algorithm applied to the incoming data stream. Its purpose is to find and save data clusters, while rejecting all noise and not interesting information. It can be disabled by programming the internal register *enable 2D* with the value 0. In this case a simple encoding is performed on input data.

The barrel shifter block has the purpose of packing the valid bits of the compressor output bus into a 30-bit register containing only valid data. The barrel block hosts an internal 60-bit long register: as soon as the 30 LSBs are ready to be put in output, the 30 MSBs are ready to accept data coming as a new input. As the last output data of an event coming from the compressor arrives, the valid bits contained in the 60-bit register are put in output padding the remaining bits with 0 when necessary.

The fifo\_data block is a flip-flop based FIFO used to buffer compressed and packed data before they are multiplexed into the 16-bit output. The FIFO contains 24 30-bit words. The FIFO is asymmetric for what concerns the I/O buses: in fact the input bus is 30-bit long and the output bus is 15-bit long. This leads to the fact that one push action is balanced by two pop actions. The FIFO contains several output flags showing the FIFO status: *empty*, *almost empty*, *half full*, *almost full* and *full*.

The almost full flag is asserted when 20 out of 24 memory locations have been written, while the half full signal is asserted when 12 out 24 locations of the FIFO are in use. Starting from these two signals, an hysteresis flag has been created: it is asserted when the FIFO gets almost full and is put back to 0 when at least half of the FIFO locations have been freed. The hysteresis flag is one of the signals that have been put in OR with each others in order to create the *data stop* output. Having a FIFO with hysteresis is very important since it allows to have a smaller number of transitions on the data stop signal with respect, for example, to the use of the almost full signal for creating data stop. This results in a higher reliability of the complete system. Thanks to the mechanism of the hysteresis flag the FIFO should never get completely full and then overflow. The hysteresis flag is also sent in input to the compressor block in order to deal with this particular situation: at the end of an event fetch, the 2D compressor sends data contained in the RAM one after the other without any back-pressure taking place. In case the data are numerous, they can be put the FIFO in overflow. In order to avoid this situation the hysteresis flag is used as a back-pressure on the 2D compressor as well.

## 2D compressor block

The 2D-compressor algorithm is essentially based on a double-threshold cluster-finding technique. Compression performances are completely tunable using a set of registers that can be programmed using a standard JTAG port. Using this port, the 2D compression itself can be switched on or off and the threshold levels can be modified by writing and reading the JTAG port.

A cluster is defined by a five cross-like 8-bit pixels structure: the five pixels, each composed of five 8-bit data, are named respectively EAST, CENTER, WEST, NORTH and SOUTH. At every clock cycle the CENTER pixel is analyzed: its value is saved if:

- at least it is higher than a low threshold;

- at least one of the five pixels of the cross is higher than the high-threshold (or higher than the low threshold if CENTER  $> T_H$ ).

In case both conditions are met, the central point of the cross is saved and encoded by means of a variable length encoder. In this way the chosen 8-bit pixels are converted into 5 to 10-bit encoded data depending on their data values. Thus, going back to the cluster finding technique, three main cases can be described:

- 1. if the cluster is detected alone, separated from others, not only the encoded data value is transferred but also its position within the matrix. This condition applies always at the beginning of a multiple cluster.

- 2. if the cluster follows a previously detected adjacent cluster, its position is already known since it is "the previous one + 1" and its position information is not transferred. This is a case of a multiple cluster where only the encoded data are transferred, apart from the first data that satisfies the threshold conditions.

- 3. if the cluster is not detected, no information is put to output.

The electronics of the 2D-compressor itself masks one or two of these five bytes to zero in case the CENTER is located onto the border of the matrix. For example in case the CENTER is located in the higher right corner the compressor sets the NORTH and EAST bytes to zero. Moreover, during the analysis of the 256-th row the compressor sets to zero the SOUTH bytes. This is in order to avoid detecting clusters even where they are not present.

At the end of each stream of data samples (up to 256) that compose each anode, the compressor sets an End Of Row Summary that summarizes the information of the anode itself. For example, occasional parity errors that may arise into CARLOS registers or during the read/write operation on the RAMs. In addition the summary specifies if the bi-dimensional compressor is active or not. Then other internal counter overflow flags are packed in the summary to be able off-line to reconstruct easily all the parameters of the physics of the event.

The CARLOS compression internal unit is mainly composed of two RAM memories and some logic. The two 256 x 9-bit words memories temporarily store the incoming

data for letting the bi-dimensional compressor analyze the potential clusters. The RAM of the compressor unit is composed of the following registers:

- an 8-bit input register storing data coming from the front-end electronics at every clock cycle;

- 2 256 x 9-bit dual-port RAM blocks RAM0 and RAM1,

- 5 8-bit registers NORTH, SOUTH, EAST, CENTER and WEST.

The data values coming from the input register are sequentially written from address 0 of the first memory RAM0 up to the address 255 of the second RAM1 and then again from the first address of the first memory. In this way the two memories are circularly written. At the same time both memories are read at the same address. In this way two rows of the incoming matrix plus one value are stored during each clock cycle, in order to determine if its center value has to be saved or rejected.

## **Disabling the 2D compressor**

When the 2D compression is disabled (*enable* 2D = 0), the following encoding on input data is performed:

| Input data range | Output code      | Bits    |

|------------------|------------------|---------|

| 0-1              | 1 bit & 000      | 4 bits  |

| 2-3              | 1 LSB bit & 001  | 4 bits  |

| 4-7              | 2 LSB bits & 010 | 5 bits  |

| 8-15             | 3 LSB bits & 011 | 6 bits  |

| 16-31            | 4 LSB bits & 100 | 7 bits  |

| 31-63            | 5 LSB bits & 101 | 8 bits  |

| 64-127           | 6 LSB bits & 110 | 9 bits  |

| 128-255          | 7 LSB bits & 111 | 10 bits |

After receiving the last data word of an event coming from AMBRA, the compressor block keeps sending in output 16 dummy words whose value depends on the data coming from AMBRA. These values have to be rejected while decoding CARLOS outputs.

# **End of Row Summary**

When the 2D compression is enabled, after processing all the samples belonging to an anode, an End of Row (EOR) Summary is sent in output. It is 21-bit long with the following format:

| E/O   | $\mathbf{VL}$ | $\mathbf{V}\mathbf{Z}$ | VH    | NCL    | NCZ    | NCH    | Parity | 001    |

|-------|---------------|------------------------|-------|--------|--------|--------|--------|--------|

| 1 bit | 1 bit         | 1 bit                  | 1 bit | 3 bits | 4 bits | 4 bits | 3 bits | 3 bits |

#### where:

**E/O**: Even / Odd anode.

**VL**: Overflow of the counter NCL, it is put to 1 if NCL reaches 7 counts within an anode;

**VZ**: Overflow of the counter NCZ, it is put to 1 if NCZ reaches 15 counts within an anode;

VH: Overflow of the counter NCH, it is put to 1 if NCH reaches 15 counts within an anode;

**NCL**: it counts the CENTER pixel values satisfying TL, but not TH.

**NCZ**: it counts the CENTER pixel values whose value is 0.

**NCH**: it counts the CENTER pixel values satisfying TH.

**Parity**: it is a 3-bit code whose meaning is explained in Table 1.

A parity error on CARLOS is detected if one of the following conditions apply:

- a parity error is detected on CARLOS internal RAMs;

- a parity error is detected on CARLOS JTAG programmable registers.

A parity error on AMBRA is detected if the MSB of AMBRA data bus (bit 8) is set to logic level 1.

| Parity | meaning                                    |

|--------|--------------------------------------------|

| 000    | no error on A & C (enable $2D = 0$ )       |

| 001    | severe error on both A & C                 |

| 010    | sever error on C, no info on A minor error |

| 011    | sever error on A, no info on C minor error |

| 100    | minor error on both A & C                  |

| 101    | minor error on C, no error on A            |

| 110    | minor error on A, no error on C            |

| 111    | no error on A & C (enable $2D = 1$ )       |

**Table 1**: Parity violation information in the EOR Summary.

with the following definitions:

- sever error: >= 7 parity errors on the samples of one anode;

- minor error: < 7 parity errors on the samples of one anode.

A severe error is also reported in bits 3-0 of the error flag words.

The EOR Summary is appended at the end oh each processed anode also when the 2D compression is disabled. In this case its format is the following one:

| 14 zeros | E/O   | Parity | 001    |

|----------|-------|--------|--------|

| 14 bits  | 1 bit | 3 bits | 3 bits |

**N.B.:** Possible parity errors occurring on the first two pixels of an anode and on the last two pixels of an anode may not be reported in the EOR Summary.

## **Data transmission protocol**

### JTAG mode

During the JTAG programming of one of the front-end devices, the JTAG answer *tdo* is sent to the GOL chip via the 16-bit bus *output\_data*. The *tdo* signal can be generated by one of the following devices:

- by the internal boundary scan block on CARLOS;

- by the PASCAL chips;

- by the AMBRA chips;

- by the GOL chip itself

depending on which is the JTAG-addressed device.

In order to sample the *tdo* value only when valid (in fact CARLOS does NOT receive any *tdo\_en* input signal), CARLOS monitors the *tms* input signal received over the serial back-link channel, in order to be always aware of the current state of the JTAG state machine. The *tdo* value will then be sampled only during the Shift-DR and Shift-IR states as foreseen by the standard IEEE 1149.1.

Three cases have been foreseen:

- when CARLOS is JTAG-addressed: the *tdo* coming from the internal boundary scan unit is sampled;

- when an other device is JTAG-addressed: the *tdo* coming from outside (either *tdo\_from\_LH* or *tdo\_from\_RH* or *tdo\_from\_GOL*) is sampled. In this case the *tdi* input sent towards CARLOS internal boundary scan unit is tied to 1: so far CARLOS internal instruction register finds a BYPASS command and no undesired change is applied on CARLOS internal registers.

- when in broadcast mode: no tdo value is sampled and put in output at all.

### When addressing PASCAL, AMBRA or CARLOS:

After being sampled, the selected *tdo* values are then stored into the *fifo\_jtag* 128x1 FIFO. Then if the *gol\_ready* signal is 1, the FIFO block is read out and the JTAG words are put in output. So far in normal conditions the FIFO is written during one clock cycle and read at the following one, so it never gets full. If the GOL PLL loses the synchronization with its incoming clock (*gol\_ready* = 0) while CARLOS is transmitting JTAG words, the *tdo* values are stored into the FIFO and remain there until the *gol\_ready* signal is asserted again. If the *gol\_ready* stays inactive for a long time (some ms), then the FIFO might overflow and JTAG programming should be run again.

## When addressing the GOL chip:

A special issue has to be dedicated to the GOL JTAG programming. After addressing the GOL chip and during its internal registers programming phase, CARLOS samples its *tdo* values (*tdo\_from\_GOL*) and stores these values into an internal memory (*fifo\_jtag*) consisting of 128 bits. The values stored into this buffer are then sent in output only after the JTAG connection towards the GOL

chip has been closed by asserting the trst signal and only if the gol ready signal is active (i.e. the GOL chip is ready to transmit data over the optical fibre). In fact when running JTAG instructions on the GOL chip, such as the Sample / Preload or Extest instructions, the chip is no longer able to transmit data. The same holds when writing GOL internal configuration registers, which may cause the PLL synchronization loss. So far during each JTAG programming stage of the GOL chip, no more than 128 bits have to be expected back as a JTAG answer; otherwise the fifo jtag block overflows and the JTAG answer gets corrupted. In the 128 bits total budget, 5 bits have to be taken into account for each instruction sent to the GOL and then n bits for the data register being accessed. For instance, 55 bits for accessing internal configuration registers and 57 bits for accessing GOL internal boundary scan chain. The CORETEST JTAG instruction can not be run on GOL, since its output can be understood only by GOL designers. All the others JTAG instructions can be run on the GOL chip. If the expected budget exceeds 128 bits, two consecutive JTAG connections towards the GOL chip can be opened and run one after the other.

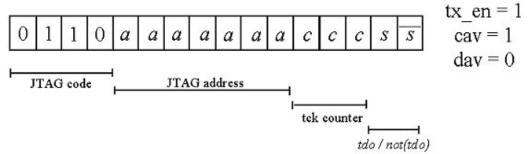

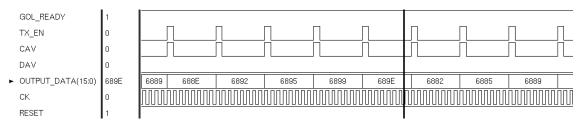

The *tdo* signal is put in output by the *Outmux* block with the following format (see Fig. 4):

- JTAG code: 0110

- JTAG address (the 7-bit word received when opening a JTAG connection)

- 3-bit counter: it is incremented for every *tdo* sample put in output

- *tdo* value

- not(*tdo*) value (in order to have a better fault tolerance)

When a JTAG word is available on the output bus, the strobe pins  $tx\_en$  and cav are asserted. In this way CARLOSrx can easily check JTAG answers and verify the correctness of the internal registers value.

Consecutive values of *tdo* in the JTAG answer have the following meaning:

- 100...0 while sending a JTAG instruction, the number of bits depends on the selected device JTAG IR length. CARLOS and GOL have 5-bit long instruction registers, while PASCAL and AMBRA have 16-bit long instruction registers.

- n bits with the register value: its length depends of the register actually being read. For instance, when loading a 9-bit register, the *tdo* signal carries out serially the old value of the register.

The JTAG answer related to the BIST output is not put in output after sending the command RUNBIST since the BIST tests the two macro-channels and the multiplexer as if it was in RUN mode. The JTAG answer is then activated again after sending the command READ BIST RESULT.

Fig. 4: JTAG answer on the data channel

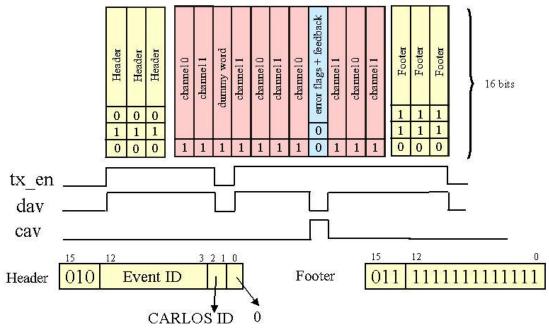

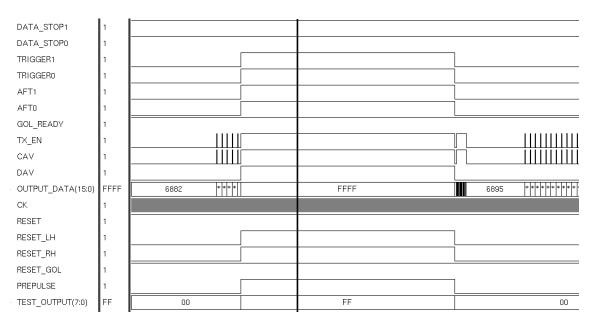

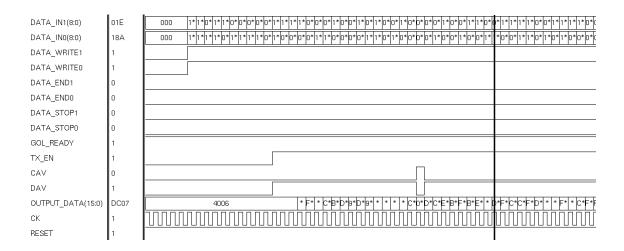

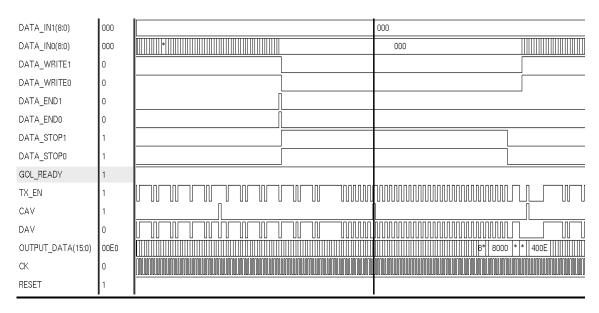

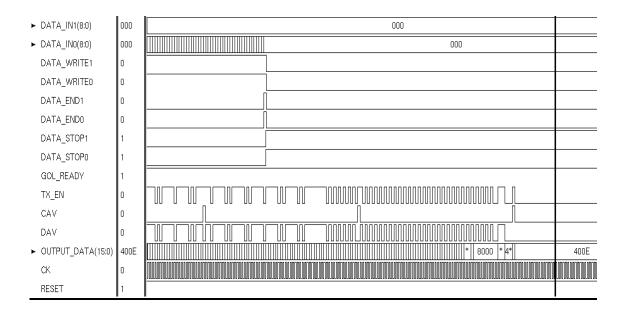

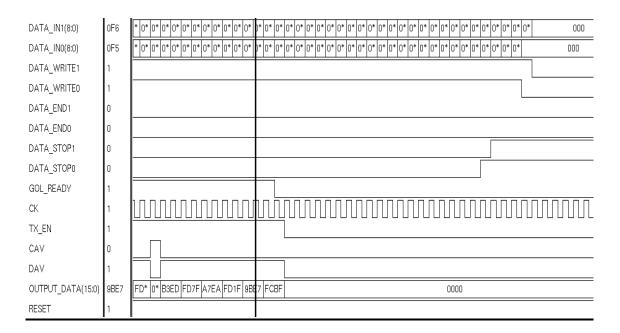

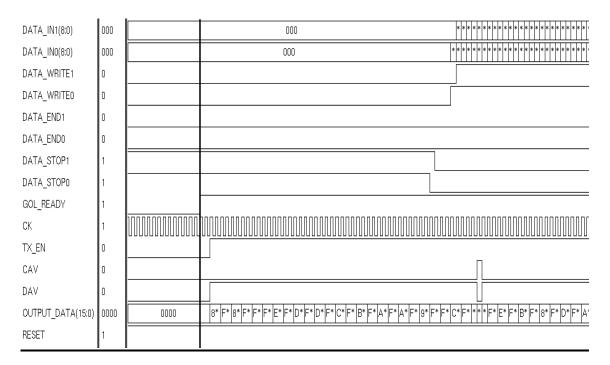

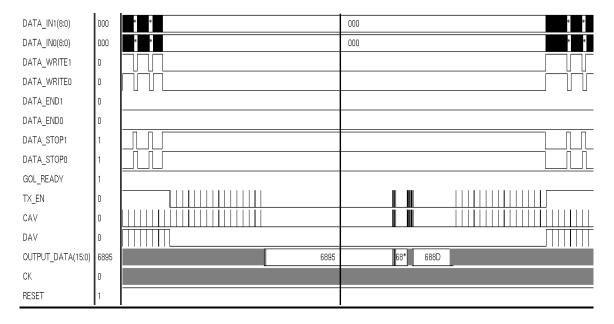

### **RUN** mode

During the JTAG mode only JTAG words are put in output.

During the RUN mode, processed data are sent in output with the protocol, shown in Fig. 5, that is compliant with both Ethernet and G-Link standard transmission protocols. The *tx\_en* strobe is used when choosing the Ethernet mode, while *cav* and *dav* signals have to be used when choosing the G-Link mode. The main difference between the two protocols on the user side is that the G-Link mode allows to distinguish data and control words with different strobe signals, while Ethernet mode implies to make this distinction directly on the 16-bit bus. In order to be able to use both protocols, we decided to identify the output words meaning using the first bits in the following way:

• MSB = 1: data word

• MSBs = 00: error flag word

MSBs = 010: header

MSBs = 0111: footer

• MSBs = 0110: JTAG word

The strobe signal  $tx\_en$  is asserted when one of the mentioned words has to be sent to the GOL chip, otherwise it is tied low.

The strobe signal *cav* is asserted when either an error flag word or a JTAG word has to be sent in output (at the same time the *dav* signal is put to 0, *cav* and *dav* are never asserted at the same time).

The strobe signal dav is asserted when a data word or header or footer has to be sent in output.

After one of the FIFOs *fifo\_data* begins receiving data from the barrel shifter block and when the *gol\_ready* signal coming from GOL is 1 (meaning that it is ready to accept input data), a new output data packet is started with 3 identical header words. The header contains a 10-bit event ID word that will be used by CARLOSrx in order to group together data coming from different detectors but belonging to the same event. The 10-bit counter is put to 0 after a reset action, then it is incremented by 1 for every data packet sent in output. The header word also contains a 2-bit CARLOS ID whose value is hardwired externally to CARLOS.

After the header words, data words from the two macro-channels are sent in output in an alternated way starting from ch0 and so on. When a channel has no data to put in output,  $tx\_en$  and dav are put to 0 and then, at the next clock cycle, the other channel sends valid output data again, if it has any. So far even in the case one channel only was used, half of the bandwidth would be allocated to the other channel.

At each rising edge of the clock CARLOS samples the *gol\_ready* signal value: when 1, CARLOS sends a valid word in output if it has any, otherwise no valid word in sent in output. For a correct data reconstruction on the CARLOSrx side, it is necessary for *gol\_ready* to stay active for an even number of clock periods, otherwise the first data after an interruption can be interpreted as belonging to the wrong channel and then cause serious misunderstanding on output data. This has been solved by generating an internal signal on CARLOS that is equal to *gol\_ready* when it stays active an even number of clock periods and stays active a period longer when *gol\_ready* stays active for an odd number of clock cycles.

### Error flag words

The error flag word is sent in output 1 every 64 clock cycles starting from the moment in which CARLOS enters the RUN mode. After an error flag word, data sent in output belongs to the opposite channel with respect to the one sending data before the error word (see Fig. 5). The error word has the following format:

| Bit #     | Description                                                        |

|-----------|--------------------------------------------------------------------|

| bit 15-14 | 00: error flag word identifier                                     |

| bit 13    | <u>L0 acknowledge</u>                                              |

|           | Asserted after receiving and decoding the L0 command on the serial |

|           | back-link.                                                         |

| bit 12    | L1reject acknowledge                                               |

|           | Asserted after receiving and decoding the L1reject command on the  |

|           | serial back-link.                                                  |

| bit 11    | <u>L2reject acknowledge</u>                                        |

|           | Asserted after receiving and decoding the L2reject command on the  |

|           | serial back-link.                                                  |

| bit 10    | prepulse acknowledge                                               |

|           | Asserted after receiving and decoding one of the prepulse commands |

|           | on the serial back-link.                                           |

| bit 9     | <u>testpulse acknowledge</u>                                       |

|           | Asserted after receiving and decoding the testpulse command on the |

|           | serial back-link.                                                  |

| bit 8     | <u>a flush action has been taken</u>                               |

|           | Asserted after the flush has been activated                        |

| bit 7     | <u>busy</u>                                                        |

|           | It is asserted after CARLOS receives a L0 command and put to 0     |

|       | when dis_trigger1 and dis_trigger0 go to 0                           |

|-------|----------------------------------------------------------------------|

| bit 6 | <u>flag error 1</u> (right hybrid)                                   |

|       | It is asserted when CARLOS detects a synchronization error with      |

|       | AMBRA on channel 1.                                                  |

| bit 5 | <u>flag error 0</u> (left hybrid)                                    |

|       | It is asserted when CARLOS detects a synchronization error with      |

|       | AMBRA on channel 0.                                                  |

| bit 4 | dis_trigger_mismatch acknowledge                                     |

|       | It is asserted when CARLOS finds a mismatch between the signals      |

|       | dis_trigger1 and dis_trigger0 coming from AMBRA.                     |

| bit 3 | parity error 1 (right hybrid)                                        |

|       | It is asserted when CARLOS detects a severe parity error on data     |

|       | coming from AMBRA RH.                                                |

| bit 2 | parity error 0 (left hybrid)                                         |

|       | It is asserted when CARLOS detects a severe parity error on data     |

|       | coming from AMBRA LH.                                                |

| bit 1 | parity error CARLOS 1 (RH)                                           |

|       | It is asserted when CARLOS detects a severe parity error on internal |

|       | RAMs or on internal JTAG programmable registers on channel 1.        |

| bit 0 | parity error CARLOS 0 (LH)                                           |

|       | It is asserted when CARLOS detects a severe parity error on internal |

|       | RAMs or on internal JTAG programmable registers on channel 0.        |

Table 2: Format of the error flag word

### bits 13-9:

When a command (L0, L1reject, L2reject, one of the prepulse commands, testpulse) is received on the serial back-link and decoded, an internal signal is asserted until an error flag word is sent in output with the corresponding bit set. Then the internal signal is put back to 0 until a new acknowledgment has to be notified to CARLOSrx.

### bit 8:

After a synchronization error between AMBRA and CARLOS requiring the use of the flush mechanism, an internal signal is asserted until an error flag word is sent in output with the corresponding bit set. Then the internal signal is put back to 0 until a new notification has to be sent.

### bit 7:

The time from the moment when CARLOS receives the trigger command and when the busy signal is asserted is not fixed. In fact it depends on the relative timing from the moment in which the trigger command is received and decoded and when the next error flag word is issued. It is a variable length period from 1 to 64 clock cycles. Then busy signal stays active for the time PASCAL needs to transfer the content of the analog memory to AMBRA or, when all AMBRA buffers are full, the time needed to empty one of the 4 buffers.

### bits 6-5:

Once asserted, the flag error remains to logic level 1 until a reset action or until CARLOS in put in JTAG mode, when Stop If Error is 1 (with the exception of the case in which the flush mechanism is activated). When Stop If Error is 0, the flag error is asserted only for one error flag word, then it is reset.

### bit 4:

If there are no connection problems, the 2 *dis\_trigger* signals coming from the left and right hybrid may differ only when the following situation occurs: when all AMBRA buffers are full, supposing that channel 1 transfers to CARLOS an event in a shorter time than channel 0, there will be a time in which one *dis\_trigger* signal is already 0 and the other one still fixed to 1. For this reason CARLOS internally performs the OR of the incoming *dis\_trigger* signal for the generation of the *busy* signal.

### bits 3-0:

Bits 3-0 of the error flag words are asserted only when a severe parity error occurs either on AMBRA or on CARLOS or on both devices. In fact when finding out 7 parity errors or more while processing data samples belonging to an anode, the related bit is asserted for the upcoming one or two error flag words. The parity error is notified in one or two error flag words depending on the timing the error is found with respect to the timing in which internal flags are sampled before being sent in output. Let's say, for example, that when processing anode number 41 and after processing 201 samples a severe error is detected; let's also suppose that an error flag word is sent in output while processing sample number 221. Since the internal flag reporting a severe parity error will be asserted until the end of the row, its value will also be sent in the forth-coming error flag word.

Fig. 5: CARLOS v5 output transmission protocol

# **CARLOS v5 pin position and function**

| Terminal name | no  | Туре | Description                                                      |

|---------------|-----|------|------------------------------------------------------------------|

| data in1(8-0) | 35- | J    | Input data bus coming from the right hybrid. The MSB is the      |

|               | 26  | _    | parity bit from AMBRA: when 1, a parity error has been           |

|               | 20  |      | detected on AMBRA.                                               |

| data in0(8-0) | 12- | I    | Input data bus coming from the left hybrid. The MSB is the       |

|               | 3   | 1    | parity bit from AMBRA: when 1, a parity error on AMBRA           |

|               |     |      | has been detected.                                               |

| data write1   | 25  | I    | Input signal coming from RH: when 1 data in1 is valid and has    |

| _             |     |      | to be accepted                                                   |

| data write0   | 2   | I    | Input signal coming from LH: when 1 data in0 is valid and has    |

| _             |     |      | to be accepted                                                   |

| data_end1     | 23  | I    | Input signal coming from RH: it is asserted in coincidence with  |

| _             |     |      | the last valid data of each event.                               |

| data end0     | 100 | I    | Input signal coming from LH: it is asserted in coincidence with  |

| _             |     |      | the last valid data of each event.                               |

| data stop1    | 24  | О    | Output signal sent to RH: when 1 it means that CARLOS can        |

| _ '           |     |      | no longer accept input data.                                     |

| data stop0    | 1   | О    | Output signal sent to LH: when 1 it means that CARLOS can        |

|               |     |      | no longer accept input data.                                     |

| trigger1      | 41  | О    | After receiving the L0 command on the serial back-link,          |

|               |     |      | trigger1 is asserted for one clock period.                       |

| trigger0      | 14  | О    | After receiving the L0 command on the serial back-link,          |

|               |     |      | <i>trigger0</i> is asserted for one clock period.                |

| aft1          | 36  | О    | Abort / flush / testpulse signal sent to RH                      |

| aft0          | 13  | О    | Abort / flush / testpulse signal sent to LH                      |

| dis_trigger1  | 22  | I    | Input from RH: when asserted no trigger signals have to be sent  |

|               |     |      | towards AMBRA                                                    |

| dis trigger0  | 99  | I    | Input from LH: when asserted no trigger signals have to be sent  |

|               |     |      | towards AMBRA                                                    |

| gol ready     | 71  | I    | Input from GOL: when asserted the GOL chip is ready to           |

|               |     |      | receive data, otherwise data transmission has to be stopped.     |

| locked        | 50  | I    | Input from QPLL: when asserted the QPLL is in locked state,      |

|               |     |      | otherwise data transmission has to be stopped.                   |

| tx en         | 47  | О    | Output strobe to GOL: when asserted the output data bus          |

|               |     |      | contains a valid data value to be transmitted.                   |

| cav           | 73  | О    | Output strobe to GOL: when asserted the output data bus          |

|               |     |      | contains a control word to be transmitted, either a JTAG word    |

|               |     |      | or an error flag word, depending on CARLOS working mode.         |

| dav           | 72  | О    | Output strobe to GOL: when asserted the output data bus          |

|               |     |      | contains a data word to be transmitted (header or footer or data |

|               |     |      | word)                                                            |

| output_data(15-0) | 70-<br>51 | О | Output bus towards GOL.                                                                                                                                                                               |

|-------------------|-----------|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ck                | 38-       | I | LVDS input clock signal.                                                                                                                                                                              |

| reset             | 44        | I | Active low reset. When active all internal registers are initialized.                                                                                                                                 |

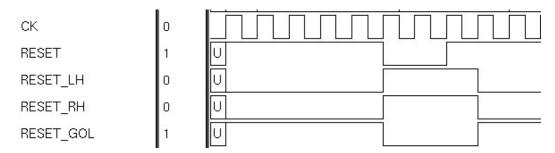

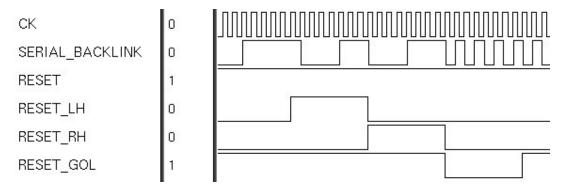

| reset_LH          | 16        | O | Active high signal towards LH. It can be asserted asynchronously by the <i>reset</i> input or synchronously when receiving the "Reset LH" command: in this case it stays active for 8 clock periods.  |

| reset_RH          | 42        | O | Active high signal towards RH. It can be asserted asynchronously by the <i>reset</i> input or synchronously when receiving the "Reset RH" command: in this case it stays active for 8 clock periods.  |

| reset_GOL         | 48        | O | Active low signal towards GOL. It can be asserted asynchronously by the <i>reset</i> input or synchronously when receiving the "Reset GOL" command: in this case it stays active for 8 clock periods. |

| ck_out            | 88        | O | The input $ck$ is directly propagated in the output signal $ck_out$ .                                                                                                                                 |

| ck_out_LH         | 86-<br>87 | О | The input $ck$ is directly propagated in the output LVDS $ck$ out $LH$                                                                                                                                |

| ck_out_RH         | 89-<br>90 | О | The input ck is directly propagated in the output LVDS ck out RH                                                                                                                                      |

| serial_backlink   | 74-<br>75 | Ι | LVDS input serial signal sending CARLOS reset, JTAG commands and trigger information using 8-bit DC-balanced codes.                                                                                   |

| tdi_to_LH         | 95        | O | Test Data Input to LH propagated to LH when a JTAG connection towards LH (or a broadcast connection) has been opened.                                                                                 |

| tms_to_LH         | 96        | 0 | Test Mode Select to LH propagated to LH when a JTAG connection towards LH (or a broadcast connection) has been opened.                                                                                |

| trst_to_LH        | 98        | О | Test Reset to LH propagated to LH when a JTAG connection towards LH (or a broadcast connection) has been opened.                                                                                      |

| tck_to_LH         | 97        | О | Test Clock to LH propagated to LH when a JTAG connection towards LH (or a broadcast connection) has been opened.                                                                                      |

| tdi_to_RH         | 18        | O | Test Data Input to RH propagated to RH when a JTAG connection towards RH (or a broadcast connection) has been opened.                                                                                 |

| tms_to_RH         | 19        | О | Test Mode Select to RH propagated to RH when a JTAG connection towards RH (or a broadcast connection) has been opened.                                                                                |

| trst to RH        | 21        | О | Test Reset to RH propagated to RH when a JTAG connection                                                                                                                                              |

| 1   | 1                                         |                                                                  |

|-----|-------------------------------------------|------------------------------------------------------------------|

|     |                                           | towards RH (or a broadcast connection) has been opened.          |

| 20  | О                                         | Test Clock to RH propagated to RH when a JTAG connection         |

|     |                                           | towards RH (or a broadcast connection) has been opened.          |

| 79  | О                                         | Test Data Input to GOL propagated to GOL when a JTAG             |

|     |                                           | connection towards GOL has been opened.                          |

| 76  | О                                         | Test Mode Select to GOL propagated to GOL when a JTAG            |

|     |                                           | connection towards GOL has been opened.                          |

| 77  | О                                         | Test Reset to GOL propagated to GOL when a JTAG                  |

|     |                                           | connection towards GOL has been opened.                          |

| 78  | О                                         | Test Clock to GOL propagated to GOL when a JTAG                  |

|     |                                           | connection towards GOL has been opened.                          |

| 17  | I                                         | JTAG answer coming from RH.                                      |

| 94  | I                                         | JTAG answer coming from LH.                                      |

| 49  | I                                         | JTAG answer coming from GOL.                                     |

| 93  | О                                         | Output signal asserted from 1 to 8 clock cycles after receiving  |

|     |                                           | the prepulse commands on the serial back-link.                   |

| 80- | I                                         | Hardwired inputs containing an information that will be put in   |

| 81  |                                           | output in the header word at the beginning of each data packet.  |

| 82, | I                                         | Test pins driving a multiplexer selection lines used to bring in |

| 84  |                                           | output internal signals coming from RAMs, compressor and         |

|     |                                           | FIFO.                                                            |

| 46- | О                                         | Internal signals put in output.                                  |

| 45  |                                           |                                                                  |

|     | 79 76 77 78 17 94 49 93 80- 81 82, 84 46- | 79 O 76 O 77 O 78 O 17 I 94 I 49 I 93 O 80- 81 82, I 84 46- O    |

# **Programming CARLOS v5**

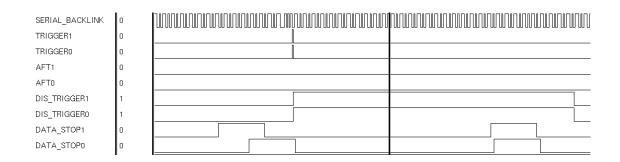

## **Controlling CARLOS via the serial back-link**

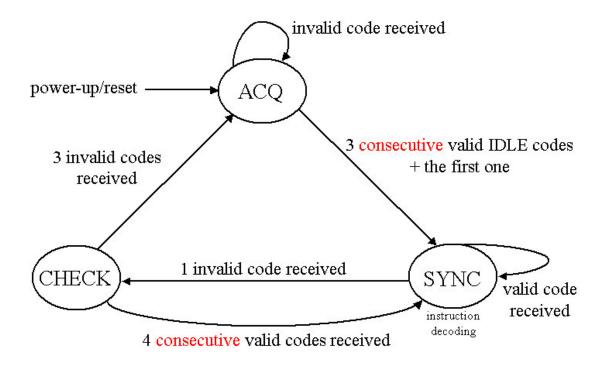

CARLOS v5 is remotely controlled using a serial back-link coming from the CARLOSrx device. Data transferred on the serial link are synchronous to the incoming 40 MHz master clock. CARLOS has a synchronization state machine which is responsible for handling link initialization and synchronization (see Fig. 6). Upon power up or external reset via the serial back-link, the state machine enters the acquisition state (ACQ) and searches for the IDLE pattern. Upon receiving three consecutive IDLE patterns after the first one, the state machine enters the synchronization state (SYNC). If an invalid code is received, the state machine transitions to the CHECK state. If, in the CHECK state, CARLOS sees 4 consecutive valid codes, the state machine acknowledges that the link is good and transitions back to the SYNC state for normal operation. If, in the CHECK state, CARLOS sees 3 invalid codes (not required to be consecutive), the state machine determines a loss of the link has occurred and transitions the synchronization state machine back to the ACQ mode. Table 3 shows the list of commands that CARLOS can receive through the serial back-link from CARLOSrx: they are all DC-balanced (same number of 1s and 0s).

Fig. 6: Synchronous serial back-link state machine decoding

| reset carlos    1100 1100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Command           | Code      | Consequence                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------|------------------------------------------|

| reset left hybrid  reset left hybrid  1100 0011  reset sent to the left hybrid (8 clock cycles long, active high)  reset right hybrid  reset GOL  1100 0101  a reset is sent to the right hybrid (8 clock cycles long, active high)  reset GOL  1100 0101  a reset is sent to the right hybrid (8 clock cycles long, active high)  reset GOL  100 0101  100 010000  100 0011  100 0011  100 0011  100 0011  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 001000  100 0010000  100 0010000  100 0010000  100 00100000  100 00100000  100 001000000  100 001000000  100 0010000000  100 00100000000                                                                                                                                                                                                                             | reset carlos      | 1100 1100 |                                          |

| reset left hybrid  reset left hybrid  1100 0011  reset sent to the left hybrid (8 clock cycles long, active high)  reset right hybrid  reset GOL  1100 0101  a reset is sent to the right hybrid (8 clock cycles long, active high)  reset GOL  1100 0101  a reset is sent to the right hybrid (8 clock cycles long, active high)  reset GOL  100 0101  100 010000  100 0011  100 0011  100 0011  100 0011  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 0010  100 001000  100 0010000  100 0010000  100 0010000  100 00100000  100 00100000  100 001000000  100 001000000  100 0010000000  100 00100000000                                                                                                                                                                                                                             |                   |           | internal blocks, except for the serial   |

| reset left hybrid  reset left hybrid  reset left hybrid  reset right hybrid  reset right hybrid  reset GOL  1100 0101  a reset is sent to the left hybrid (8 clock cycles long, active high)  reset GOL  1100 0101  a reset is sent to the right hybrid (8 clock cycles long, active high)  reset GOL  L0  1010 1100  1010 1100  1010 1100  1010 1100  1010 1100  1010 1100  1010 1100  1010 1010  1010 1010  1010 1010  1010 1010  1010 1010  1010 1010  1010 1010  1010 1010  1010 1010  1010 1010  1010 1010  1010 1010  1010 1010  1010 1010  1010 1010  1010 1010  1010 1010  1010 1010  1010 1010  1010 1010  1010 1010  1010 1010  1010 1010  1010 1010  1010 1010  1010 1010  1010 1010  1010 1010  1010 1010  1010 1010  1010 1010  1010 1010  1010 1010  1010 1010  1010 1010  1010 1010  1010 1010  1010 1010  1010 1010  1010 1010  1010 1010  1010 1010  1010 1010  1010 1010  1010 1010  1010 1010  1010 1010  1010 1010  1010 1010  1010 1010  1010 1010  1010 1010  1010 1010  1010 1010  1010 1010  1010 1010  1010 1010  1010 1010  1010 1010  1010 1010  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 1000  1010 10000  1010 100000  1010 10000  1010 10000  1010 10000  1010 10000  1010 10000  1 |                   |           |                                          |

| reset left hybrid  reset right hybrid  reset right hybrid  reset GOL  1100 0101  a reset is sent to the left hybrid (8 clock cycles long, active high)  reset GOL  1100 0101  a reset is sent to the GOL chip (8 clock cycles long, active high)  a reset is sent to the GOL chip (8 clock cycles long, active low)  L0  1010 1100  1010 1100  1010 1100  1010 1100  1010 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010  1011 1010 101 101                                                                   |                   |           |                                          |

| reset right hybrid solock cycles long, active high) reset GOL 1100 0101 a reset is sent to the right hybrid (8 clock cycles long, active high) reset GOL 1100 0101 a reset is sent to the GOL chip (8 clock cycles long, active low)  L0 1010 1100 trigger1 and trigger0 signals are activated  L1reject 1010 0011 aft1 and aft0 are asserted for 1 clock cycle cycle  L2reject 1010 1010 aft1 and aft0 are asserted for 1 clock cycle test pulse 1010 1001 aft1 and aft0 are asserted for 3 clock cycle prepulse25 1001 0011 prepulse output is asserted for 1 clock cycle towards the charge injectors prepulse50 1001 0101 prepulse output is asserted for 2 clock cycles towards the charge injectors prepulse75 1001 0110 prepulse output is asserted for 3 clock cycles towards the charge injectors prepulse100 1001 1001 prepulse output is asserted for 3 clock cycles towards the charge injectors prepulse100 1001 1001 prepulse output is asserted for 4 clock cycles towards the charge injectors prepulse125 1001 1010 prepulse output is asserted for 5 clock cycles towards the charge injectors prepulse150 1001 1100 prepulse output is asserted for 6 clock cycles towards the charge injectors prepulse150 1001 1100 prepulse output is asserted for 7 clock cycles towards the charge injectors prepulse200 1110 0001 prepulse output is asserted for 7 clock cycles towards the charge injectors prepulse output is asserted for 8 clock cycles towards the charge injectors prepulse output is asserted for 8 clock cycles towards the charge injectors prepulse output is asserted for 8 clock cycles towards the charge injectors prepulse output is asserted for 8 clock cycles towards the charge injectors prepulse output is asserted for 8 clock cycles towards the charge injectors prepulse output is asserted for 8 clock cycles towards the charge injectors prepulse output is asserted for 8 clock cycles towards the charge injectors prepulse output is asserted for 8 clock cycles towards the charge injectors prepulse output is asserted for 8 clock cycles towards the charge injec | reset left hybrid | 1100 0011 |                                          |

| hybrid reset GOL 1100 0101 a reset is sent to the GOL chip (8 clock cycles long, active high)  L0 1010 1100 trigger1 and trigger0 signals are activated  L1reject 1010 0011 aft1 and aft0 are asserted for 1 clock cycle  L2reject 1010 1010 aft1 and aft0 are asserted for 1 clock cycle  test pulse 1010 1001 aft1 and aft0 are asserted for 1 clock cycles  prepulse25 1001 0011 prepulse output is asserted for 1 clock cycle towards the charge injectors prepulse50 1001 0101 prepulse output is asserted for 2 clock cycles towards the charge injectors prepulse75 1001 010 prepulse output is asserted for 3 clock cycles towards the charge injectors prepulse100 1001 1001 prepulse output is asserted for 3 clock cycles towards the charge injectors prepulse125 1001 1010 prepulse output is asserted for 4 clock cycles towards the charge injectors prepulse125 1001 1010 prepulse output is asserted for 5 clock cycles towards the charge injectors prepulse150 1001 1100 prepulse output is asserted for 6 clock cycles towards the charge injectors prepulse150 1001 1100 prepulse output is asserted for 7 clock cycles towards the charge injectors prepulse200 1110 10001 prepulse output is asserted for 7 clock cycles towards the charge injectors prepulse200 1110 1000 prepulse output is asserted for 8 clock cycles towards the charge injectors used for link synchronization only and when there is no command to send enter JTAG 1101 0010 CARLOS enters JTAG mode enter RUN mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                   | ·         |                                          |

| reset GOL 1100 0101 a reset is sent to the GOL chip (8 clock cycles long, active low)  L0 1010 1100 trigger1 and trigger0 signals are activated  L1reject 1010 0011 aft1 and aft0 are asserted for 1 clock cycle  L2reject 1010 1010 aft1 and aft0 are asserted for 1 clock cycle  test pulse 1010 1001 aft1 and aft0 are asserted for 1 clock cycle  prepulse25 1001 0011 prepulse output is asserted for 1 clock cycle towards the charge injectors prepulse50 1001 0101 prepulse output is asserted for 2 clock cycles towards the charge injectors prepulse100 1001 1001 prepulse output is asserted for 3 clock cycles towards the charge injectors prepulse100 1001 1001 prepulse output is asserted for 3 clock cycles towards the charge injectors prepulse125 1001 1010 prepulse output is asserted for 5 clock cycles towards the charge injectors prepulse150 1001 1100 prepulse output is asserted for 6 clock cycles towards the charge injectors prepulse150 1001 1100 prepulse output is asserted for 7 clock cycles towards the charge injectors prepulse200 1110 0001 prepulse output is asserted for 7 clock cycles towards the charge injectors prepulse200 1110 1000 prepulse output is asserted for 8 clock cycles towards the charge injectors idle 0011 1001 used for link synchronization only and when there is no command to send enter RUN mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | reset right       | 1100 1010 | a reset is sent to the right hybrid (8   |

| L1 cycles long, active low)  L0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | hybrid            |           |                                          |

| L1 cycles long, active low)  L0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | reset GOL         | 1100 0101 | a reset is sent to the GOL chip (8 clock |