PageContent

Selected designs of the Bologna Electronics Centre

LUCROD: Readout board for LHC experiments at Cern

- VME 9U standard with 10 Intel Cyclone IV FPGAs

- 16 analog channels with 12 bit digital conversion up to 500MS with programmable offset and gain

- 16 analog output channels with programmable offset and gain

- 4 NIM / TTL inputs / outputs

- 2 2Gb optical transceivers

- Housing for a Cern TTCrq card

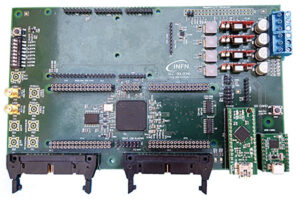

Polar-FPGA: Data acquisition card, designed for low power cosmic ray telescopes

- 1 FPGA Intel Cyclone V

- Up to 32 LVDS inputs

- 2 USB serial

- Interfaceable with Raspberry Pi, Arduino and GPS modules

- Housing for a daughter card with Cern HPTDC chip

![GSPSv2 Digitizer with Analog Input Board [FAMU] GSPSv2 Digitizer with Analog Input Board [FAMU]](/elettronica/wp-content/uploads/sites/14/2021/03/digitizer-gspsv2-300x200.jpg)

GSPSv2 Digitizer with Analog Input Board [FAMU]

- 8-channel analog-to-digital conversion card

- 4 AD9684 dual channel ADC: 14 bit, 500 MS / s

- architecture configurable via analog mezzanines that allow interlacing

- control system with Enclustra Mercury + XU1 with Xilinx’s Zynq UltraScale + ™ MPSoC

- interfaces: 2 Gigabit Ethernet, USB 3.0, Display Port, SATA

![HW switch Box board [ATLAS] HW switch Box board [ATLAS]](/elettronica/wp-content/uploads/sites/14/2021/03/hw-switch-300x200.jpg)

HW switch Box board [ATLAS]

- Multiplexer HV box with programmable selection of the single output channels, for the measurement of the IV curves necessary for the qualification tests of hybrid modules of the ITk tracer.

160 x 160 x 51.5 mm

![Orbital Detector Card [FAMU] Orbital Detector Card [FAMU]](/elettronica/wp-content/uploads/sites/14/2021/03/orbital-detector-300x200.jpg)

Orbital Detector Card [FAMU]

- Front-end electronics for 6 LaBr3-based detectors coupled with Hamamatsu high quantum efficiency photomultipliers (PMTs)

- Arrangement of RADIAL components on the entire board

- Semi-circular PCB designed for HV up to 1500V

- Baseline Restorer for each single PMT

- Management of all parameters by remote controlled Teensy 3.5 microcontrollers

366 x 183 mm

High rate breakout board with Samtec Firefly connectors (Arcadia)

- Firefly ECUE 4-Connector FMC Connector Conversion Board

- 48 differential lines with a rate of 640 Mbps

- 8 layers

69 x 60 mm

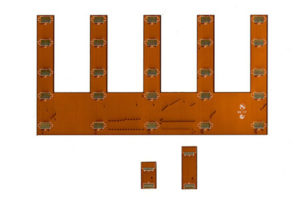

![Rigid-flexible SiPM Flex board for SiPM matrices [Grant SipMat] Rigid-flexible SiPM Flex board for SiPM matrices [Grant SipMat]](/elettronica/wp-content/uploads/sites/14/2021/03/sipm-flex-300x200.jpg)

Rigid-flexible SiPM Flex board for SiPM matrices [Grant SipMat]

- PCB FLEX 4 Layers in Kapton

- Impedance controlled tracks

- Assembly of the BGA chip (containing 64 SiPM) and connectors on Kapton

- Operation in a cryogenic environment

458 x 33 x 0.368mm

![SIPM_AMPLI [SHIP] SIPM_AMPLI [SHIP]](/elettronica/wp-content/uploads/sites/14/2020/05/SIPM_AMPLI-300x200.jpg) SIPM_AMPLI [SHIP]

SIPM_AMPLI [SHIP]

- 2 channels – 2 amplification stages: 46 dB

- 60 mm flex – 90 mm rigid

![OPTICAL_RECEIVER_32CH [DARKSIDE] OPTICAL_RECEIVER_32CH [DARKSIDE]](/elettronica/wp-content/uploads/sites/14/2020/05/OPTICAL_RECEIVER_32CH-300x200.jpg)

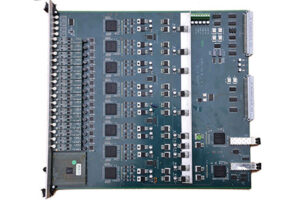

OPTICAL_RECEIVER_32CH [DARKSIDE]

- 9U size (160×360)

- 32 optical analog inputs

- 32 outputs over MCX connectors

- 64 op-amps

![]()

Silicon Germanium Bipolar RF Transistor [NU@FNAL]

- Vcc=3V I= 12mA

- Bandwidth ≈ 300MHz

- G= 23dB

- noise : ~160µV @ 1MHz (≈ 6nV/√Hz)

![Scheda MOTHERBOARD STRIP [DARKSIDE] Scheda MOTHERBOARD STRIP [DARKSIDE]](/elettronica/wp-content/uploads/sites/14/2020/05/Scheda-MOTHERBOARD-STRIP-300x200.jpg)

Scheda MOTHERBOARD STRIP [DARKSIDE]

- Kapton PCB (232×220 mm2) with blind vias

32 Channel Readout board (Nessie)

- Sensor: SiPM SensL 30035FC 3×3 mm2

- 32 channels

- Input: triaxial cable (~ 1.5 m)

- EASIROC (ampli – shaping/fast trigger analog serial out

- FPGA: Altera Cyclone III EP3C16Q240C8N (EASIROC and USB handling – data processing for SiPM calibration/monitoring)

- Out : USB – EASIROC Analog (to Digitizer)

- Main purpose: fast SiPM acquisition – low level signals ( ⪝ mV)

- Critical design issues:

- custom pitch of input connectors

- signal integrity of PCB traces to EASIROC

- filtering and isolation of all power sections

- 6 Layers – 10 boards (so far)

150 x 100 mm

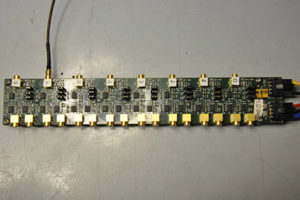

CATB (Ship)

- Sensor: Several SiPM from AdvanSiD (FBK Spin-Off) and Hamamatsu

- Test Board mainly aimed to timing studies (goal: resolution < 1 ns)

- 8 channels

- Input: coaxial cable (~2 m)

- Pre-amplification :1 fast out and 1 slow per channel

- 4 layer – 2 boards

- Out : to Digitizer

- Small-size coaxial connectors (MCX)

224 x 38 mm

Photo_Chain (A.Montanari)

- Sensor: SI Photodiode Hamamatsu S1087/S1133 series

- 4 channels

- INFN Patent

150 x 36 mm

PMT HV Divider (FAMU)

- Sensor: LaBr3 scintillator + PMT

- Active voltage-divider, amplification, power supply

- Unique schematic engineered on 5 distinct PCB due to geometrical detector requirements

- Layout with PADS (Mentor Graphics)

- 2 layers – 20×5 samples

- Critical issues:

- cooling (needs carefully component partition to the 5 PCB)

- connections engineering (multi-board 3D view with PADS)

every board: 45 x 45 mm

Motherboard (Darkside)

- Sensor: SiPM

- Board Purpose: collect signals from front-end devices

- Requirement:

- good thermal behavior (immersed in Liquid Nitrogen @ ~ -190 °C)

- low-radioactivity material

- the very first design of the electronics Center made in Kapton

- Critical design issues:

- SiPM signal integrity (controlled impedance striplines between two ground planes)

- stackup and material selection

- 4 Layers – 3 samples (so far)

- Designed with PADS (Mentor Graphics)

- Signal integrity simulated with HyperLynx (Mentor Graphics)

215 x 114 mm

DPP (FAMU)

- Input: 1 analog-digital conversion channel

- AD8138: differential input buffer (-3dB BW @ 320 MHz) acting also as anti-aliasing filter

- ADC: AD9434 12bit @ 500 MS/s (ENOB: 10.5 up to 250 MHz input – 1.5 Vpp)

- FPGA Altera Cyclone V 5CGXC5 (digital filtering and data acquisition)

- Output: Piggy Back Cypress USB 3.0 (max datarate: 5 Gb/s)

- 6 layers – 11 board

- Critical issue: accordion for high-speed USB3 signal from FPGA to Piggy Back connector

65 x 130 mm

Digitizer Board (Nucl-Ex)

- Input: 2 analog-digital conversion channels

- Anti-aliasing filter (simulated with SPICE)

- ADC: AD9255BCPZ-125 14bit @ 125 MS/s (ENOB: 12 up to 250 MHz input – 2 Vpp)

- Digital Signal Processor: ADSP-2189NKCAZ-320

- 6 layers – 50 mezzanine

- Critical issues:

- input from 100 mV to 8 V (managed with multiple voltage controlled amplifiers and analog multiplexers)

- variable gain and offset (controlled with separated DACs)

140 x 55 mm

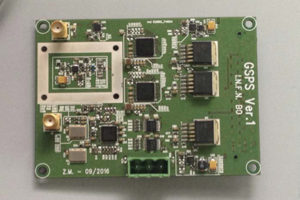

GSPS (Elec.Division R&D)

- FMC mezzanine Card

- Input: 1 analog-digital conversion channel with 2 interleaved ADC

- ADA4930 differential buffer coupled in DC with single ended input (6 dB gain)

- Anti-aliasing filter (simulated with SPICE)

- ADC: AD9434 12bit @ 500 MS/s (ENOB: 10.5 up to 250 MHz input – 1.5 Vpp)

- Output: 12 LVDS x ADC through FMC connector

- 6 layers – 2 cards

- Critical issues:

- filter design

- low-jitter clock distribution ( < 1 ps RMS)

- reconstruction firmware

98 x 70 mm

![]()

IBL/PIXEL ROD (Atlas)

- Input : 32 FE-I4 (160 Mb/s per channel – 5.12 Gb/s in total )

- Control, Data Taking, Monitoring and Calibration

- 14-layer 9U x 400 mm VME64x board

- 1 Xilinx Spartan6 XC6SLX45-FGG484

- 1 Xilinx Virtex5 XC5VFX70T-FF1136: (embedded PowerPC HW core)

- 2 GByte DDR2 SODIMM

- 64 Mbit FLASH Atmel AT45DB642D

- 2 Xilinx Spartan6 XC6SLX150-FGG900:

- 1 2-Gbit DDR2 (Mictor MT47H128M16RT-25E)

- 2 1Mx36 SSRAM (Cypress CY7C1370D-250AXC-ND)

- Cal: 3 Gbit Ethernet interfaces (PHY: DP83865)

- Output: 4 S-Links (5.12 Gb/s in total)

360 x 400 mm

DRM2 (ALICE)

- Input : TRM board (TDC data from MRPC detector) output through VME

- Data Taking, Control, Trigger interface (80 boards foreseen for ’19 Alice upgrade)

- 14 layers – 9U x 160 mm – 5 samples so far (foreseen : ~80)

- GBTx from CERN (rad-hard) : serdes @ 4.8 Gb/s

- FPGA: Microsemi Igloo 2 M2GL90T

- Output: GBTx (~ 3.2 Gb/s user payload)

- Critical issues:

- GBTx handling (interface IP core from CERN has been tested yet)

- Serdes

345 x 162 mm

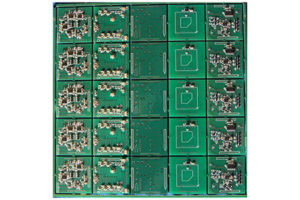

PMT Voltage Divider (Limadou)

- Sensor: Hamamatsu R9880U

- Limadou calorimeter with Plastic Scintillators

- Critical issues:

- Small PCBs/ high voltages : discharges risk

- Outgassing

- Thermal resistance (made with Kapton-Polyamide)

- Redundancy (doubling capacitors)

32 x 20 mm

FMC mezzanine for DU Base (Km3NET)

- Near-communication interface board: between the Central Logic Board (CLB) and electronics into (close to) the DU Base

- RS422, RS485, custom protocol on RJ45, FMC to the CLB

- 5 boards so far (foreseen : ~ 100)

- Critical issues:

- galvanic insulation (AC coupling)

- component reliability

- FMC connector mechanics

70 x 50 mm